#### CMOS 8-Bit Microcontroller

## TMP88CH47N, TMP88CH47F

TMP88CH47N is high-speed and high-function 8-bit single-chip microcomputers whose built-in features include large-capacity RAM, multi-function timer/counter, and 10-bit AD converter, serial interface (UART/I2C bus). They are equipped with 3 phase brushless DC sensorless/sensor motor control, and AC motor inverter control.

| Part No.   | ROM       | RAM        | Package           | OTP MCU    |

|------------|-----------|------------|-------------------|------------|

| TMP88CH47N | 16K bytes | E12 by dag | P-SDIP42-600-1.78 | TMP88PH47N |

| TMP88CH47F | Tok bytes | 512 bytes  | P-QFP-1414-0.80D  | TMP88PH47F |

#### **Features**

- ▶8-bit single-chip microcomputer TLCS-870/X series microcomputer

- Interrupt sources: 23 (5 external, 18 Internal)

- ◆I/O ports: 34 pins

- Large-current output: 8 pins (typ. 20 mA), LED direct drive

- ▶ 16-bit timer/counter: 2 channels

- Timer, event counter, programmable pulse generator (PPG) output, pulse width measurement, external trigger timer, window mode

- ◆8-bit Timer/Counter: 1 channel

- Timer capture (pulse width measurement), programmable divider output (PDO) mode

- ◆Time base timer (interrupt frequency: 1 to 16384 Hz)

- ◆Watchdog timer

- Divider output function (frequency: 1 to 8 kHz)

- Programmable motor driver (PMD): 1 channel

- Rotor position: minimum resolution of 250 ns for detecting rotor position

- Motor control timer, timer capture function

- Overload protection function DC overload protection function AC overload protection function

- (Can halt counter in 3-phase PWM output circuit)

- Protection circuit for malfunction (urgent halt)

- Automatic direction change, automatic position detection start

- Serial interface

- 8-bit SIO/I<sup>2</sup>C bus

- Universal asynchronous receiver transmitter (UART)

- 10-bit successive approximation type AD converter

- Analog input: 8 channels

- Conversion time: 11.5  $\mu$ s/46  $\mu$ s (at 16 MHz operation)

- Low power dissipation operation (2 modes)

- STOP mode: Stops oscillation (battery or capacitor backup). Port output hold or high impedance selectable

- IDLE mode: Stops CPU but continues operation of peripheral hardware. Released by interrupt (restarts CPU)

- ◆Operating voltage: 4.5 to 5.5 V at 16 MHz operation

980910EBP2

TMP88CH47N

TMP88PH47N

TMP88CH47F

TMP88PH47F

- 980910EBP2

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

Purchase of TOSHIBA I<sup>2</sup> C components conveys a license under the Philips I<sup>2</sup> C Patent Rights to use these components in an I<sup>2</sup> C system, provided that the system conforms to the I<sup>2</sup> C Standard Specification as defined by Philips.

> 3-47-1 1999-09-29

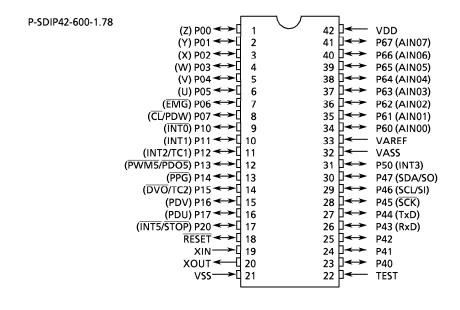

P-SDIP42-600-1.78

P-QFP44-1414-0.80D

## **Pin Assignments**

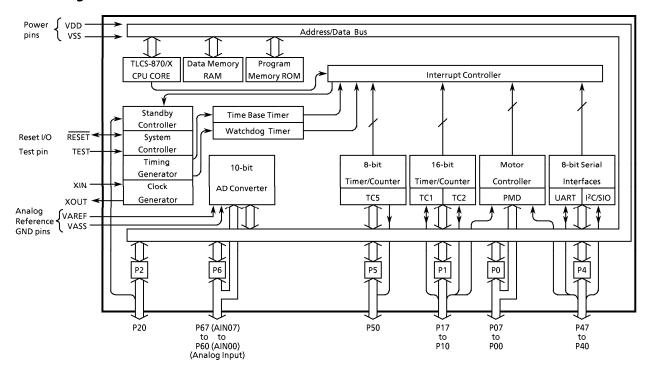

### **Block Diagram**

# **Pin Function**

| Pin Name                | 1/0                 | Fun                                                                                | ction                                                                             |

|-------------------------|---------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| P07 (CL/PDW)            | W2 (1)              | 8-bit programmable I/O port (tri state)<br>Input or output specifiable in units of | Overload protection input /motor control circuit W-phase position detection input |

| P06 (E <u>MG</u> )      | ··· I/O (Input)     | bits.  When using pins for motor control                                           | Motor control circuit malfunction detection input                                 |

| P05 (U)                 |                     | circuit, set accordingly using POCR, then MDCR to 1.                               | Motor control circuit U-/V-/W-phase                                               |

| P04 (V)                 | I/O (Output)        |                                                                                    | output                                                                            |

| P03 (W)                 |                     |                                                                                    |                                                                                   |

| P02 (X)                 |                     |                                                                                    | Motor control circuit X-/ Y-/Z-phase output                                       |

| P01 (Y)                 | I/O (Output)        |                                                                                    | datpat                                                                            |

| P00 (Z)                 |                     |                                                                                    |                                                                                   |

| P17 (PDU)               | W2 (1)              | 8-bit programmable I/O port (tri state) Input or output specifiable units of bits. | Motor control circuit U-phase position detection input                            |

| P16 (PDV)               | ··· I/O (Input)     | When using pins for motor control circuit, timer/counter input, or external        | Motor control circuit V-phase position detection input                            |

| P15 (DVO/TC2)           | II/O (Output/Input) | interrupt input, set them to input mode.                                           | Divider output or Timer/Counter 2 input                                           |

| P14 (PPG)               |                     | When using pins for PPG output, divider output, or PWM output/PDO output, set      | Programmable pulse generator output                                               |

| P13 (PWM5/PDO5)         | ··· I/O (Output)    | them to output mode.                                                               | PWM5 output/PDO5 output                                                           |

| D12 (INIT2/TC1)         |                     |                                                                                    | External interrupt input 2 or                                                     |

| P12 (INT2/TC1)          | I/O (Input)         |                                                                                    | Timer/Counter 1 input                                                             |

| P11 (INT1)              |                     |                                                                                    | External interrupt input 1                                                        |

| P10 ( <del>INT0</del> ) |                     |                                                                                    | External interrupt input 0                                                        |

| Pin Name                      | 1/0              | Fun                                                                                                                                                                                | ction                                                        |  |  |

|-------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| P20 (INT5/STOP)               | I/O (Input)      | 1-bit I/O port When using pins for input port, external interrupt input, or STOP mode release input, set output latches to 1.                                                      | External interrupt input 5 or STOP mode release signal input |  |  |

| P47 (SDA/SO)                  | I/O (I/O/Output) | 8-bit I/O port                                                                                                                                                                     |                                                              |  |  |

| P46 (SCL/SI)                  | I/O (I/O/Input)  | When using pins for motor control                                                                                                                                                  | 12C/SIO I/O                                                  |  |  |

| P45 (SCK)                     | I/O (I/O)        | circuit input, UART/I <sup>2</sup> C/SIO, set output latches to 1.                                                                                                                 |                                                              |  |  |

| P44 (TxD)                     | I/O (Input)      | lateries to 1.                                                                                                                                                                     | UART data input                                              |  |  |

| P43 (RxD)                     | I/O (Output)     |                                                                                                                                                                                    | UART data output                                             |  |  |

| P42                           |                  |                                                                                                                                                                                    | _                                                            |  |  |

| P41                           | 1/0              |                                                                                                                                                                                    | _                                                            |  |  |

| P40                           |                  |                                                                                                                                                                                    | <u> </u>                                                     |  |  |

| P50 (INT3)                    | I/O (Input)      | 1-bit input/output port with latch. When using pins for input port, HPWM output, PWM output/PDO output, external interrupt input, or timer/counter input, set output latches to 1. | External interrupt 3 input                                   |  |  |

| P67 (AIN07)<br>to P60 (AIN00) | I/O (Input)      | 8-bit programmable I/O port (tri state) Input or output specifiable in units of bits.  When using pins for analog input, set to input mode using P6CR and ADCCR.                   | AD converter analog input                                    |  |  |

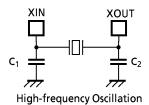

| XIN, XOUT                     | Input, Output    | High-frequency oscillator connecting pins and leave XOUT open.                                                                                                                     | . For external clock input, input to XIN                     |  |  |

| RESET                         | I/O              | Reset signal input, watchdog timer output, address trap reset output, system clock reset output                                                                                    |                                                              |  |  |

| TEST                          | Input            | Shipment test pin. Fix to "L" level.                                                                                                                                               |                                                              |  |  |

| VDD, VSS                      | Danier Court     | + 5 V, 0 V (GND)                                                                                                                                                                   |                                                              |  |  |

| VAREF, VASS                   | Power Supply     | Analog reference voltage for AD conversion. Reference GND.                                                                                                                         |                                                              |  |  |

#### **Operation**

### 1. CPU Core Functions

The CPU core consists of the CPU, system clock control circuit, and interrupt control circuit. This chapter describes the CPU core, program memory, data memory and the reset circuit.

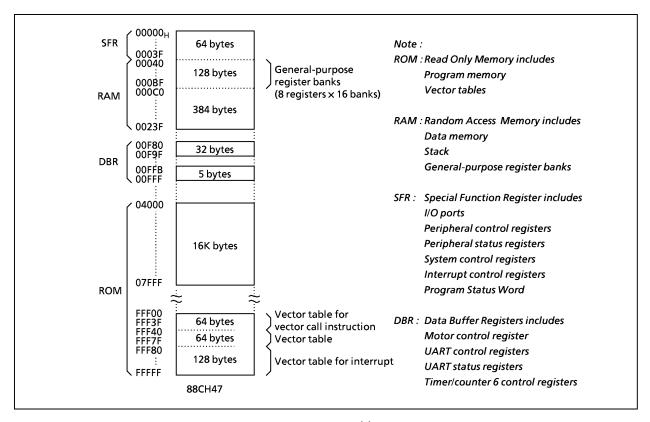

#### 1.1 Memory Address Map

The TMP88CH47 memory consists of four blocks: ROM, RAM, special function registers (SFR) and Data buffer registers (DBR). They are all mapped to a 1M-byte address space. Figure 1-1 shows the TMP88CH47 memory address map. There are 16 general-purpose registers mapped to the RAM address space.

Figure 1-1. Memory Address Maps

### 1.2 Program Memory (ROM)

TMP88CH47 contains a 16K-byte program memory (mask ROM) at addresses from 04000 to 07FFF<sub>H</sub>. In addition, contains a 256-byte program memory (mask ROM) at addresses from FFF00 to FFFFF<sub>H</sub>.

#### **Electrical Characteristics**

Absolute Maximum Ratings  $(V_{SS} = 0 V)$

| Parameter                       | Symbol             | Pins                                 | Ratings                        | Unit |

|---------------------------------|--------------------|--------------------------------------|--------------------------------|------|

| Supply Voltage                  | $V_{DD}$           |                                      | - 0.3 to 6.5                   | ٧    |

| Input Voltage                   | V <sub>IN</sub>    |                                      | - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Valtana                  | V <sub>OUT1</sub>  | Port P21, P22, RESET, Tri-state port | - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |

| Output Voltage                  | V <sub>OUT2</sub>  | Port P20, Sink open drain port       | – 0.3 to 5.5                   | ٧    |

|                                 | I <sub>OUT1</sub>  | Ports P1, P2, P4, P5, P6             | 3.2                            |      |

| Output Current                  | I <sub>OUT2</sub>  | Port P0                              | 20                             | mA   |

|                                 | Σl <sub>OUT1</sub> | Ports P1, P2, P4, P5, P6             | 120                            |      |

| Output Current                  | ΣΙ <sub>ΟUΤ2</sub> | Port P0                              | 60                             | mA   |

| Power Dissipation [Topr = 70°C] | PD                 | TMP88CH47                            | 600                            | mW   |

| Soldering Temperature (time)    | Tsld               |                                      | 260 (10 s)                     | °C   |

| Storage Temperature             | Tstg               |                                      | – 55 to 125                    | °C   |

| Operating Temperature           | Topr               |                                      | - 40 to 85                     | °C   |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

Recommended Opeating Conditions

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter          | Symbol           | Pins                    | C                                     | Conditions                                         |                        | Max                    | Unit |

|--------------------|------------------|-------------------------|---------------------------------------|----------------------------------------------------|------------------------|------------------------|------|

| Supply Voltage     | V <sub>DD</sub>  |                         |                                       | fc = NORMAL mode 16 MHz IDLE mode                  |                        | 5.5                    | V    |

|                    |                  |                         |                                       | STOP mode                                          |                        |                        |      |

|                    | V <sub>IH1</sub> | Except hysteresis input | V >4.5V                               |                                                    | V <sub>DD</sub> × 0.70 |                        |      |

| Input High Voltage | V <sub>IH2</sub> | Hysteresis input        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | V <sub>DD</sub> ≥ 4.5 V<br>V <sub>DD</sub> < 4.5 V |                        | V <sub>DD</sub>        | >    |

|                    | V <sub>IH3</sub> |                         | V                                     |                                                    |                        |                        |      |

|                    | V <sub>IL1</sub> | Except hysteresis input |                                       | ~                                                  |                        | V <sub>DD</sub> × 0.30 |      |

| Input Low Voltage  | V <sub>IL2</sub> | Hysteresis input        | V                                     | V <sub>DD</sub> ≧4.5 V                             |                        | V <sub>DD</sub> × 0.25 | V    |

|                    | V <sub>IL3</sub> |                         | V                                     | V <sub>DD</sub> <4.5 V                             |                        | V <sub>DD</sub> × 0.10 |      |

| Clock Frequency    | fc               | XIN, XOUT               | V <sub>DD</sub> :                     | = 4.5 to 5.5 V                                     | 8.0                    | 16.0                   | MHz  |

Note 1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note 2: Clock frequency fc: The condition of supply voltage range is the value in NORMAL and IDLE modes.

D.C. Characteristics

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                     | Symbol           | Pins                             | Conditions                                                         | Min | Тур. | Max | Unit |

|-------------------------------|------------------|----------------------------------|--------------------------------------------------------------------|-----|------|-----|------|

| Hysteresis Voltage            | V <sub>HS</sub>  | Hysteresis inputs                |                                                                    | _   | 0.9  | _   | V    |

|                               | I <sub>IN1</sub> | TEST                             |                                                                    |     |      |     |      |

| Input Current                 | I <sub>IN2</sub> | Sink open drain, Tri-state ports | $V_{DD} = 5.5 \text{ V}$<br>$V_{IN} = 5.5 \text{ V/0 V}$           | _   | _    | ± 2 | μΑ   |

|                               | I <sub>IN3</sub> | RESET, STOP                      | VIN = 3.3 V/O V                                                    |     |      |     |      |

| Local Bushes (#)              | R <sub>IN</sub>  | TEST with pull-down              |                                                                    |     | 70   | 170 |      |

| Input Resistor (*)            |                  | RESET                            |                                                                    | 90  | 220  | 510 | kΩ   |

| Output Leakage<br>Current     | I <sub>OL</sub>  | Sink open drain, Tri-state ports | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V/0 V              | -   | -    | ± 2 | μΑ   |

| Output High<br>Voltage        | V <sub>OH</sub>  | Tri-state ports                  | $V_{DD} = 4.5 \text{ V}, \ I_{OH} = -0.7 \text{ mA}$               | 4.1 | _    | -   | V    |

| Outside Commit                | I <sub>OL1</sub> | Except XOUT, Ports P0            | $V_{DD} = 4.5 \text{ V}, \ \ V_{OL} = 0.4 \text{ V}$               | _   | 1.6  | _   |      |

| Output Low Current            | I <sub>OL2</sub> | Port P0                          | V <sub>DD</sub> = 4.5 V, V <sub>OL</sub> = 1.0 V                   | _   | 10   | _   | mA   |

| Supply Current in NORMAL Mode |                  |                                  | V <sub>DD</sub> = 5.5 V                                            | _   | 20   | 32  | mA   |

| Supply Current in IDLE Mode   |                  |                                  | $V_{IN} = 5.3 \text{ V}/0.2 \text{ V}$<br>fc = 16.0 MHz            | _   | 10   | 16  | mA   |

| Supply Current in STOP Mode   |                  |                                  | $V_{DD} = 5.5 \text{ V}$<br>$V_{IN} = 5.3 \text{ V}/0.2 \text{ V}$ | _   | 0.5  | 20  | μΑ   |

Note 1: Typical values show those at Topr =  $25^{\circ}$ C,  $V_{DD} = 5 V$ .

Note 2: Input Current  $l_{IN1}$ ,  $l_{IN3}$ ; The current through registor is not included, when the input resistor (pull-up or pull-down)

is contained.

Note 3: IDD except I<sub>REF</sub>.

AD Conversion Characteristics

$(Topr = -40 \text{ to } 85^{\circ}C)$

|                          |                  |                                                           |                       |      | Max             |            |         |             |

|--------------------------|------------------|-----------------------------------------------------------|-----------------------|------|-----------------|------------|---------|-------------|

| Parameter                | Symbol           | Conditions                                                | Min                   | Тур. | ADCDR1          | ADC        | ADCDR2  |             |

|                          |                  |                                                           |                       |      | ADCDRI          | ACK = 0    | ACK = 1 |             |

| V <sub>ARE</sub>         |                  | ., ., ., ., ., ., ., ., ., ., ., ., ., .                  | V <sub>DD</sub> – 1.0 |      | V <sub>DD</sub> |            |         |             |

| Analog Reference Voltage | V <sub>ASS</sub> | V <sub>AREF</sub> – V <sub>ASS</sub> ≧ 3.5 V              | V <sub>SS</sub>       | 1    |                 | 1.0        |         | V           |

| Analog Input Voltage     | V <sub>AIN</sub> |                                                           | V <sub>ASS</sub>      | _    |                 | $V_{AREF}$ |         | <b>&gt;</b> |

| Analog Supply Current    | I <sub>REF</sub> | V <sub>AREF</sub> = 5.5 V,<br>V <sub>ASS</sub> = 0.0 V    | _                     | 0.5  |                 | 1.0        |         | mA          |

| Non-Linearity Error      |                  |                                                           |                       | 1    | ± 1             | ± 3        | ± 2     |             |

| Zero Point Error         |                  | $V_{DD} = 5.0 \text{ V}, V_{SS} = 0.0 \text{ V}$          | _                     | 1    | ± 1             | ± 3        | ± 2     |             |

| Full Scale Error         |                  | V <sub>AREF</sub> = 5.000 V<br>V <sub>ASS</sub> = 0.000 V | _                     | _    | ± 1             | ± 3        | ± 2     | LSB         |

| Total Error              |                  |                                                           |                       | _    | ± 2             | ± 6        | ± 4     |             |

Note 1: ADCDR1: 8-bit AD conversion result (1LSB =  $\Delta V_{AREF}$ /256)

ADCDR2: 10-bit AD conversion result (1LSB =  $\Delta V_{AREF}$ /1024)

Note 2: Total error includes all errors except quantization error.

A.C. Characteristics

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, Topr = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                   | Symbol           | Conditions                   | Min   | Тур. | Max  | Unit |

|-----------------------------|------------------|------------------------------|-------|------|------|------|

| Machine Cycle Time          | tov              | NORMAL mode                  | 0.25  | -    | 0.5  | . •  |

| Machine Cycle Time          | tcy              | IDLE mode                    | 0.25  |      |      | μS   |

| "H" Level Clock Pulse Width | t <sub>WCH</sub> | For external clock operation | 31.25 |      | 62.5 | ns   |

| "L" Level Clock Pulse Width | t <sub>WCL</sub> | (XIN input)                  | 31.23 | 1    | 02.5 | 115  |

**Recommended Oscillating Conditions**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, Topr = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                     | Oscillator        | Oscillation | Recommended Oscillator | Recommended Constant |                |  |

|-------------------------------|-------------------|-------------|------------------------|----------------------|----------------|--|

| rarameter Oscillator          |                   | Frequency   | Recommended Oscillator | C <sub>1</sub>       | C <sub>2</sub> |  |

| High-frequency<br>Oscillation | Ceramic Resonator | 16 MHz      | MURATA CSA16.00 MXZ    | 5pF                  | 5pF            |  |

|                               |                   |             | MURATA CST16.00 MXW    | built-in 5pF         | built-in 5pF   |  |

Note: An electrical shield by metal shield on the surface of IC package should be recommendable in order to prevent the device from the high electric fieldstress applied from CRT (Cathode Ray Tube) for continuous reliable operation.